Yapay zeka süratle gelişirken, bu alanda kullanılan donanım tahlilleri de büyük bir dönüşüm yaşıyor. Bilhassa yüksek bant genişlikli bellekler (HBM), hem eğitim hem de çıkarım süreçlerinde büyük değere sahip. Fakat daldaki talep artışı, mevcut HBM tedarik zincirini zorlarken, alternatif teknolojilere olan muhtaçlığı da beraberinde getiriyor. Bu bağlamda Intel, SoftBank ve Tokyo Üniversitesi dikkat alımlı bir iş birliğine imza attı: Yeni teşebbüs “Saimemory“, yapay zeka hızlandırıcıları için klâsik HBM tahlillerine alternatif oluşturacak bir bellek teknolojisi geliştirmeyi hedefliyor.

Yapay zeka süratle gelişirken, bu alanda kullanılan donanım tahlilleri de büyük bir dönüşüm yaşıyor. Bilhassa yüksek bant genişlikli bellekler (HBM), hem eğitim hem de çıkarım süreçlerinde büyük değere sahip. Fakat daldaki talep artışı, mevcut HBM tedarik zincirini zorlarken, alternatif teknolojilere olan muhtaçlığı da beraberinde getiriyor. Bu bağlamda Intel, SoftBank ve Tokyo Üniversitesi dikkat alımlı bir iş birliğine imza attı: Yeni teşebbüs “Saimemory“, yapay zeka hızlandırıcıları için klâsik HBM tahlillerine alternatif oluşturacak bir bellek teknolojisi geliştirmeyi hedefliyor. Daha verimli ve ölçeklenebilir bellek

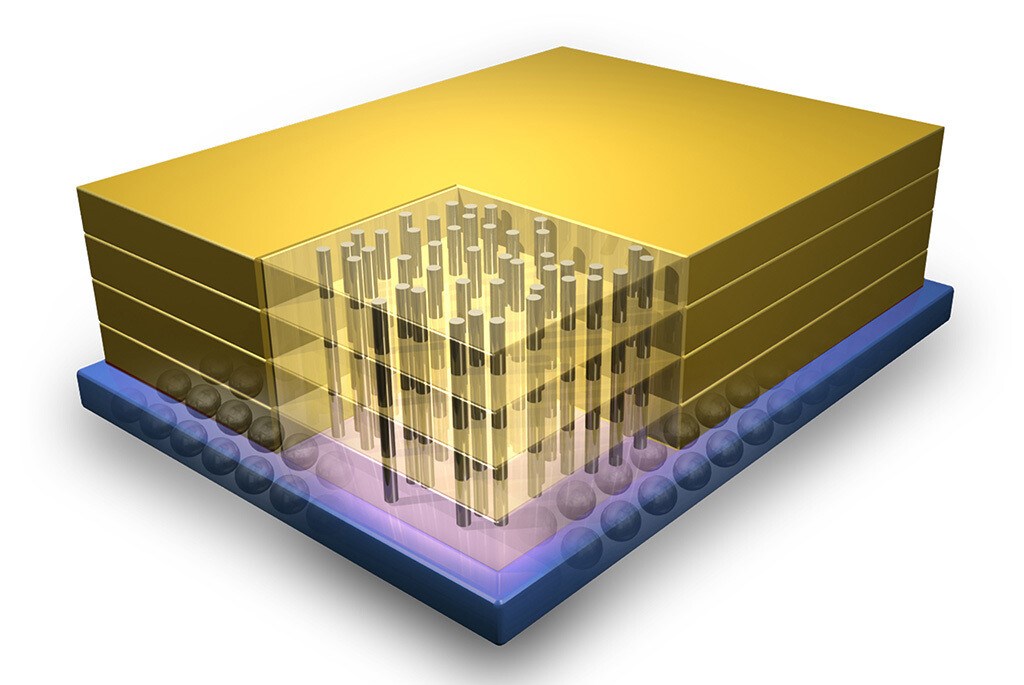

Saimemory teşebbüsü, istiflenmiş DRAM mimarisini temel alarak HBM’ye rakip bir yapı geliştirmeye odaklanıyor. Teşebbüsün birinci prototiplerinin 2027 yılında hazır olması beklenirken, hacimli üretim maksadı 2030 yılı olarak belirlenmiş durumda. Projede Intel’in çip dizaynındaki deneyimi, Tokyo Üniversitesi’nin yenilikçi bellek patentleriyle buluşuyor. SoftBank ise Ar-Ge sürecine yaklaşık 3 milyar yen (yaklaşık 21 milyon dolar) fon sağlayarak projeye finansal takviye sunuyor.

Şimdi resmi olarak doğrulanmasa da Japonya merkezli Riken Araştırma Enstitüsü ve Shinko Electric Industries üzere kurumların da teşebbüse teknik ortak ya da yatırımcı olarak katılması gündemde. Ayrıyeten, geliştirme sürecini hızlandırmak için Japon hükümetinden dayanak alınması da planlanıyor.

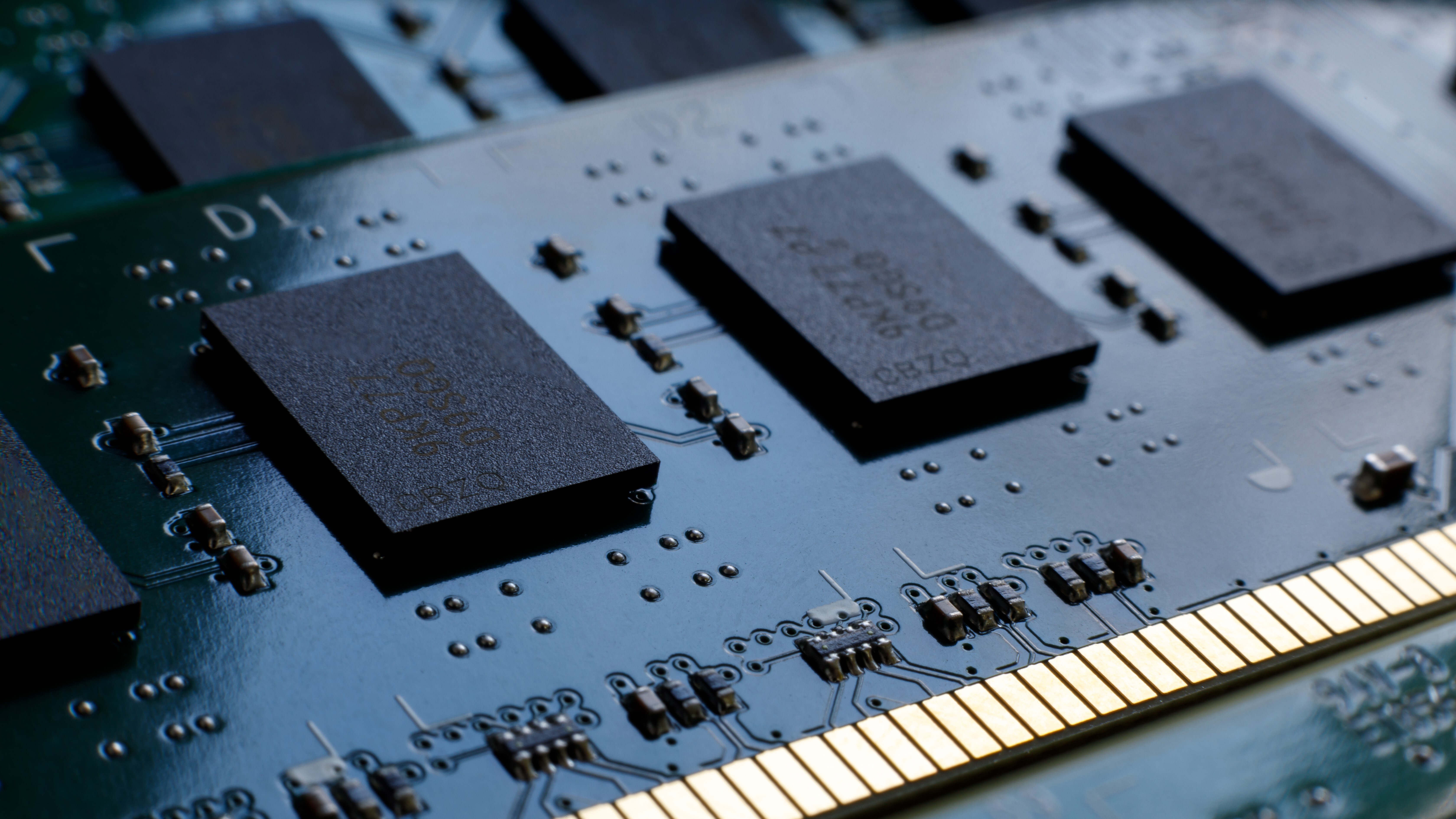

Şimdi resmi olarak doğrulanmasa da Japonya merkezli Riken Araştırma Enstitüsü ve Shinko Electric Industries üzere kurumların da teşebbüse teknik ortak ya da yatırımcı olarak katılması gündemde. Ayrıyeten, geliştirme sürecini hızlandırmak için Japon hükümetinden dayanak alınması da planlanıyor. Günümüzde kullanılan klâsik HBM teknolojisi, DRAM katmanlarının dikey olarak birbirine bağlandığı TSV (Through-Silicon Via) yapısını ve geniş data yolu içeren interposer mimarisini temel alıyor. Bu sayede saniyede 1 TB ve üzeri bilgi transfer suratlarına ulaşılabiliyor. Fakat bu yapı yüksek maliyetli, üretimi karmaşık ve güç tüketimi açısından sınırlayıcı olabiliyor.

Saimemory’nin geliştirdiği yeni bellek mimarisi, sinyal yönlendirme ve bellek tazeleme idaresinde esaslı değişiklikler sunarak yüzde 50’ye varan güç verimliliğinin yanı sıra gecikme süresi ve genel performansta iyileşme vaat ediyor.

Geçmişte denendi, başarılamadı

2011 yılında Samsung ve Micron’un birlikte geliştirdiği “Hybrid Memory Cube” (HMC) teknolojisi de benzeri formda HBM’ye alternatif olmayı hedeflemişti. DDR3’e nazaran 15 kata kadar daha yüksek suratlar vaat eden HMC, birinci etapta daldan takviye görse de 2018 yılında üretimi durduruldu. Münasebetiyle tek başına bir alternatif yetmiyor, standart haline gelmiş bir eserin yerini alabilecek kadar cazip olmak gerekiyor. Saimemory başarılı olursa, teknolojinin birinci kullanıcısı büyük olasılıkla Intel’in yapay zeka hızlandırıcıları olacaktır.